프로젝트 지도교수 연구실 소개

ARC 연구실 (Architecture and Code Optimization)

컴퓨터공학부 이재욱 교수님

교수님 약력

○ 학력

- 박사(Ph.D., 2009) : MIT Electrical Engineering & Computer Science (CS Division)

- 석사(M.S., 2002) : Stanford University Electrical Engineering

- 학사(B.S., 1999) : 서울대학교 전기공학부

○ 경력

- (2016 ~ 현재) : 부교수, 서울대학교 컴퓨터공학부

- (2011 ~ 2016) : 조교수, 성균관대학교 반도체시스템공학과

- (2011) : Postdoctoral Research Associate, CS Department, Princeton University

- (2009 ~ 2011) : Researcher and Engineer, Parakinetics, Inc. (Princeton, USA)

- (2002 ~ 2009) : Research Assistant, MIT CSAIL

- (2008) : Graduate Exchange Scholar, EECS Department, UC Berkeley

- (2006, 2007) : Research Intern, Nokia Research Lab in Cambridge (NRCC)

- (2002) : Engineering Intern, Nvidia Corp.

연구분야 및 연구실 소개

○ 연구분야

- 컴퓨터 아키텍처 (특히, AI 및 Big Data 응용을 위한 HW/SW 플랫폼 설계)

- 시스템 소프트웨어

○ 연구실 소개

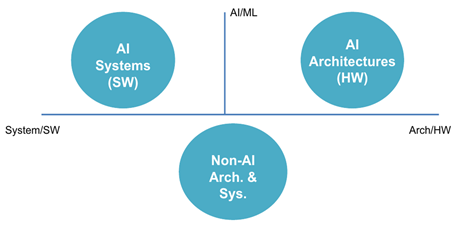

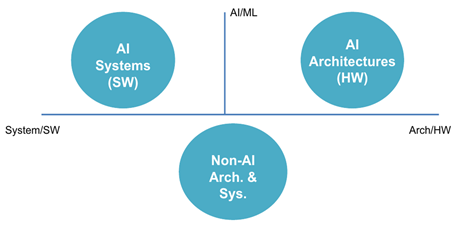

ARC 연구실은 기본적으로 컴퓨터를 설계하는 연구실입니다. Hardware(HW) Side와 Software(SW) Side 모두에서 컴퓨터를 보다 빠르고 효율적으로 만드는 연구를 하고 있습니다. 주요 연구 분야는 아래의 그림과 같이, System/SW부터 Architecture/HW까지의 컴퓨터 분야 영역과 AI/ML인지 아닌지에 따라 Domain을 구분하여 크게 세 가지의 Focus Area로 나눌 수 있습니다.

[ARC 연구실의 Focus Area]

최근 진행한 연구를 중심으로 보다 구체적인 소개를 하자면, 다음과 같습니다.

첫 번째 AI Architecture 연구로써 Machine Learning(ML) 응용분야의 폭발적인 확산에 따라 기존의 CPU를 활용한 범용 컴퓨터로는 원하는 성능/전력/비용 등의 요구를 달성 할 수 없기에 ARC 연구실에서는 Machine Learning(ML)을 가속화하기 위한 Specialized HW를 만들고, 거기에 대한 SW까지 Co-design함으로써 이를 해결하고자 합니다.

다음으로 Non-AI Architecture에 대한 연구도 활발히 진행되고 있는데, Non-AI 분야인 데이터센터, 모바일/엣지/IoT에서도 Technology Scaling 둔화로 인해 범용 컴퓨터로는 원하는 성능/전력/비용 등의 요구를 달성 할 수 없습니다. 이에, Big Data 처리(특히 검색, 데이터 분석 등)를 위한 다양한 가속기 Architecture와 이를 지원하기 위한 SW Framework를 개발하고 있습니다.

ARC 연구실은 HW분야뿐만 아니라, SW분야에 대한 연구도 활발히 하고 있습니다. 상술한 바와 같이, ML, Big Data 응용의 확산으로 메모리/스토리지 수요는 폭발적으로 증가하고 있으나, 기존의 SW Stack은 성능/전력/비용 요구를 감당하지 못하고 있습니다. 이러한 한계를 극복하기 위한 새로운 SW Stack Design을 연구하고 있습니다.

주요 프로젝트

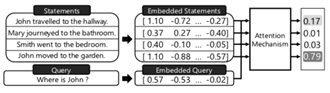

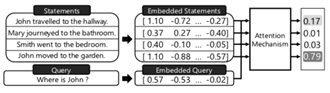

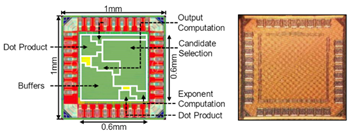

○ A3 Attention Mechanism Accelerator [HPCA’20]

- Attention determines what is relevant to the input query through content-based similarity search.

. Decides what to attend: Used in NLP (like BERT), Q&A systems (like MemN2N), Vision, etc.

Q&A System Example

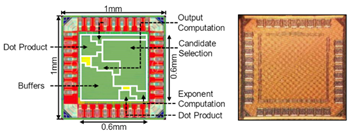

A3 Test Chip (TSMC 40nm)

A specialized hardware chip that accelerates attention mechanism.

☞ >100x more Performance/Watt than CPU and GPU.

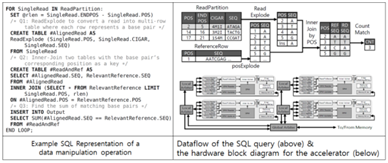

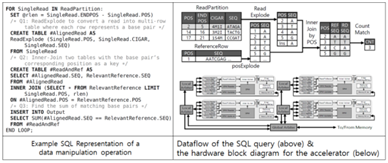

○ Genesis: A Cloud FPGA Accelerator of Genomic Data Analysis [ISCA’20a]

- Gene sequencing pipeline consists of multiple stages including data manipulation operations.

- Genesis lets users to describe their target data manipulation operation in SQL and constructs a hardware accelerator for the operation using pre-constructed HW module.

☞ 기존 CPU 대비 2-18배에 달하는 성능 향상과 2-15배의 비용 절감을 달성

[Genesis SQL 연산 표현 예(좌) 및 이를 구현한 FPGA 가속기(우)]

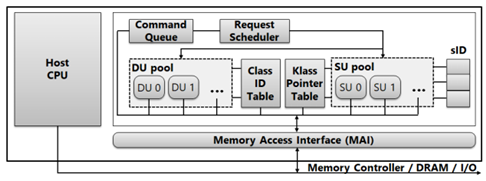

○ Cereal: Specialized architecture for object serialization [ISCA’20b]

- 모든 메모리 오브젝트를 순차적으로 탐색하고 처리하는 기존 알고리즘을 개선하여, 이들을 효과적으로 병렬처리 할 수 있는 새로운 직렬화 포맷을 제안하고, 이 개선된 알고리즘을 수행하는 가속기 하드웨어 설계

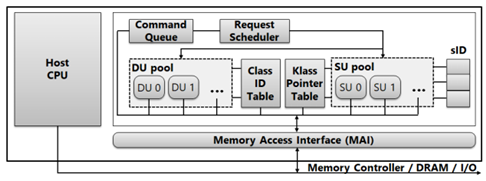

[Cereal 가속기 Architecture]

☞ Apache Spark 응용 수행 시 Java Serializer 대비 평균 7.9배, Kryo 대비 평균 4.8배의 (역)직렬화 성능 향상을 달성

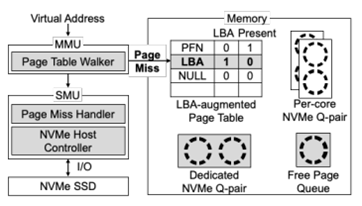

○ Hardware-assisted demand paging [ISCA’20c]

- 페이지 폴트가 발생했을 때, 기존의 OS가 예외를 처리하는 대신, CPU 캐시 미스 처럼 예외 발생 없이 이를 파이프라인에서 직접 처리하는 기술

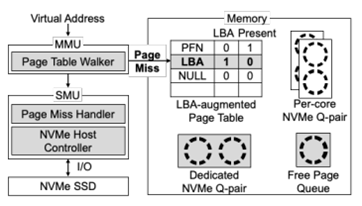

[Cereal 가속기 Architecture]

☞ OS 커널에서 낭비되는 CPU 사이클을 제거하여, OS에서 제공하는 페이지 보호 기능을 유지하면서 디스크 액세스 시간에 가까운 페이지 폴트 처리시간을 제공

○ IIU:Inverted index search accelerator [ASPLOS’20]

○ Charon: Specialized architecture for garbage collection [MICRO’19]

○ FlashNeuron:SSD-enabled large-batch training of very deep neural networks [USENIX ATC’20]

○ Practical erase Suspension for modern low-latency SSDs [USENIX ATC’19a]

○ Asynchronous I/O stack: Low-latency kernel I/O stack for ultra-Low latency SSDs [USENIX ATC’19b]

○ Portable, automatic data quantizer for deep neural networks [PACT’18]

성과

○ Press Release

- 컴퓨터 아키텍처 분야의 플래그십 컨퍼런스인 제47회 ACM/IEEE International Symposium on Computer Architecture(ISCA)에 3편의 논문 게재 (2020)

- 시스템 분야 최고 우수 학회 중 하나인 USENIX Annual Technical Conference(ATC) 2019에 총 3편의 논문 게재 (2019)

- 반도체 회로 설계 분야 최우수 학회인 IEEE Symposium on VLSI Circuits(초고집적 회로 심포지엄)에서 “10년간 최다 피인용 논문상 수상” (2017)

○ Publications (2017 ~ 2020)

- Yeonhong Park, Seung Yul Lee, Hoon Shin, Jun Heo, Tae Jun Ham, and Jae W. Lee, "Unlocking Wordline-level Parallelism for Fast Inference on RRAM-based DNN Accelerator", 39th IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Diego, California, November 2020.

- Yeonhong Park, Woosuk Kwon, Eojin Lee, Tae Jun Ham, Jung Ho Ahn, and Jae W. Lee, "Graphene: Strong yet Lightweight Row Hammer Protection", 53rd IEEE/ACM International Symposium on Microarchitecture (MICRO-53), Athens, Greece, October 2020.

- Jaeyoung Jang, Sung Jun Jung, Sunmin Jeong, Jun Heo, Hoon Shin, Tae Jun Ham, Jae W. Lee, “A Specialized Architecture for Object Serialization with Applications to Big Data Analytics”, The 47th ACM/IEEE International Symposium on Computer Architecture (ISCA), June 2020.

- Tae Jun Ham, David Bruns-Smith, Brendan Sweeney, Yejin Lee, Seong Hoon Seo, U Gyeong Song, Young H. Oh, Krste Asanovic, Jae W. Lee, Lisa Wu, “Genesis: A Hardware Acceleration Framework for Genomic Data Analysis”, The 47th ACM/IEEE International Symposium on Computer Architecture (ISCA), June 2020.

- Gyusun Lee*, Wenjing Jin*, Wonsuk Song, Jeonghun Gong, Jonghyun Bae, Tae Jun Ham, Jae W. Lee, Jinkyu Jeong, “A Case for Hardware-based Demand Paging”, The 47th ACM/IEEE International Symposium on Computer Architecture (ISCA), June 2020.

- Jun Heo, Jaeyeon Won, Yejin Lee, Shivam Bharuka, Jaeyoung Jang, Tae Jun Ham, Jae W. Lee, “IIU: Specialized Architecture for Inverted Index Search”, ACM Architectural Support for Programming Languages and Operating Systems (ASPLOS), March 2020.

- Tae Jun Ham, Sung Jun Jung, Seonghak Kim, Young H. Oh, Yeonhong Park, Yoon Ho Song, Junghoon Park, Sanghee Lee, Kyoung Park, Jae W. Lee, Deog-Kyoon Jeong, “A3: Accelerating Neural Network Attention Mechanism with Approximation”, IEEE International Symposium on High-Performance Computer Architecture (HPCA), February 2020.

- Jaeyoung Jang, Jun Heo, Yejin Lee, Jaeyeon Won, Seonghak Kim, Sung Jun Jung, Hakbeom Jang, Tae Jun Ham, Jae W. Lee, “Charon: Specialized Near-Memory Processing Architecture for Clearing Dead Objects in Memory”, IEEE/ACM International Symposium on Microarchitecture (MICRO), Oct, 2019.

- Jonghyun Bae, Hakbeom Jang, Jeonghun Gong, Wenjing Jin, Shine Kim, Jaeyoung Jang, Tae Jun Ham, Jinkyu Jeong and Jae W. Lee, “SSD Streamer: Specializing I/O Stack for Large-Scale Machine Learning”, IEEE Micro, Sept/Oct 2019.

- Gyusun Lee, Seokha Shin, Wonsuk Song, Tae Jun Ham, Jae W. Lee and Jinkyu Jeong, “Asynchronous I/O Stack: A Low-latency Kernel I/O Stack for Ultra-Low Latency SSDS”, USENIX Annual Technical Conference(ATC), July 2019.

Shine Kim, Jonghyun Bae, Hakbeom Jang, Wenjing Jin, Jeonghun Gong, Seungyeon Lee, Tae Jun Ham, and Jae W. Lee, “”Practical Erase Suspension for Modern Low-latency SSDs, USENIX Annual Technical Conference(ATC), July 2019.